# An Advanced Modified Cascaded Switch-Ladder Multilevel Inverter Structure

<sup>1</sup>P.Natarajan, <sup>2</sup>G.Ganesan @ Subramanian, <sup>3</sup>R.Anandaraj

<sup>1</sup>P.G Student, <sup>2,3</sup>Assistant Professor, Dept. Of Electrical and Electronics Engineering, E.G.S Pillay

Engineering College, Nagapattinam, India

#### aecraj@gmail.com

*Abstract*— An Advanced Modified Cascaded Switch-Ladder Multilevel Inverter Structure is presented and it generates an optimum number of voltage output levels. Firstly, a fundamental switch-ladder multilevel structure is described. Then, the structure of recommended cascaded topology based on series connection of fundamental switch ladder topologies is presented. To generate optimum number of levels with minimum number of switching elements, dc sources and voltage on switches, the proposed cascade topology is modified for better results. After a detailed evaluation of the results, it is proven that the proposed cascaded topology involves lesser number of components. In addition to that the value of voltage rating on switches is lesser compared to existing system. Test outcomes for two topologies are analysed to verify the performance of proposed topology. Matlab simulink model is used to evaluate the performance of cascaded switch-ladder multi level inverter topology.

Keywords: Multilevel Inverter Operation, Optimization, Cascaded switch-Ladder, Voltage level.

## I. INTRODUCTION

Multilevel inverters have several applications. These devices are cost effective. As technology advances at a faster rate, it is not possible to avoid the usage of power conditioning devices. Since multilevel inverters are used in lot of scenarios, it is the rule of thumb to enhance the structure of these devices with regard to bringing down in numbers the components and voltage rating ion switches. Some of the conventional Multi level inverters are the cascaded H-bridge inverter(CHB) , the neutral-pointclamped inverters and flying capacitors. Flying capacitor inverters provide switch combination redundancy for balancing different voltage levels. Both real and reactive power flow can be controlled. These broadly studied and readily available Multilevel inverters are instrumental in aiding for high-quality ac supplies and motor drivers in industrial application due to their good performance. The duty cycle of both switches is controlled in such a way that in one input, multi-output DC-AC inverters the voltage on all output capacitors are adjusted to same voltages. Lower total harmonic distortion(THD) is needed in high voltage induction motor drives. In the existing system, 13 levels were used in the multi level inverter. In the proposed system, 15 levels are used. One switch has been added as compared to existing system. Source levels are even. In the existing system, input voltage is 1-1-2-2. In the proposed system, the input voltage has been changed as 1-1-2-3. 15 levels are output.

## **II. RELATED WORKS**

This chapter briefly discusses the development of non linear transcendental Selective Harmonic Elimination (SHE) equation problem in control of multilevel inverter with an objective of controlling the chosen multilevel inverter configuration during whole range of modulation index from 0 to 1 with less % THD which complies with IEEE 519-1992 harmonic guidelines and also with less switching losses. Commercially existing topologies of multilevel inverters and modulation strategy for the control of multilevel inverters are briefly reviewed. It also reviewed the research progress of various techniques for solving non linear transcendental SHE equation problem. This chapter also presents the objective of research, research methodology and the thesis organization.

#### A BRIEF REVIEW OF MULTILEVEL INVERTER TOPOLOGIES

Now-a-days, power requirements of modern industries have reached to megawatt level. In particular, high-power medium voltage drives requires power in megawatt range and is usually connected to the medium voltage network. It is troublesome to connect a single power semiconductor switch directly to medium voltage grid (2.3kV,3.3kV, 4.16kV or 6.9 kV). For this reasons, multilevel inverter have emerged as a cost effective solution for high voltage and high power applications including power quality and motor drive problems [26]. As a cost effective solution, multilevel converter not only achieves higher voltage and current ratings, but also enables the use of low power application in renewable energy sources. These converters are suitable in high voltage and high power applications due to their ability to synthesize higher voltages with a limited maximum device rating, less harmonic distortion,

producing of smaller common-mode voltage (CM), less electromagnetic compatibility (EMC) problems and attain higher voltage with a limited maximum device rating.At present, multilevel inverters are extensively used in various applications such as HVDC transmission [27], distribution generation systems[28], medium voltage motor drives[29], Flexible AC Transmission System (FACTS) , traction drive systems, var compensation and stability enhancement, active filtering, chemical, liquefied natural gas (LNG) plants, marine propulsion, electric vehicle systems (EVS), hybrid electric vehicle systems(HEV) and adjustable speed drives. The range of the output power is a very important and evident limitation of two-level inverter. However, this problem can be overcome by introducing the concept of multilevel converters in 1975. The concept of multilevel began with the three-level converter which is often known as neutral-point converter (NPC). The word "converter" refers to the power flow in both the directions i.e. from ac to dc called as "rectifier" and from dc to ac called as "inverter". The word "multilevel inverter" refers to using a multilevel converter in the inverting mode of operation. In order to meet the challenges such as high dv/dt causing voltage doubling effect in motor output voltage waveform, % THD to comply with IEEE 519-1992 harmonic guidelines, high electromagnetic interference (EMI), high common-mode voltages and requirements of synthesizing higher voltages for modern industrial applications have subsequently led the development of various inverter topologies. The commercially existing inverter topologies are neutral point clamped (NPC) inverter, flying capacitor (FC) and cascaded H-bridge (CHB) inverter topologies and are briefly reviewed in next section.

#### Neutral-Point Clamped (NPC) or Diode-Clamped Topology

One of the traditionally accepted and widely used for various industrial and power sector topology applications is neutral point converter which was proposed by Nabae, Takahashi and Akagi in 981. As the two-level inverter has the drawback of achieving higher power levels with the available GTOs of 4.5kV voltage rating at that time, for traction applications, three-level inverter configuration was developed to meet the requirement of high voltage dc operation in traction application in Austrian railways. Three-level neutral point converter often called as three-level diode-clamped inverter has found wide range application because of advantages such as higher power handling the capability, less dv/dt and less %THD when compared to conventional two-level inverter. Later, direct extensions of the original NPC for higher number of levels are presented by several researchers in 1990s and presented experimental results for the applications such as variable motor drives, static var compensation and medium voltage systems interconnections. The diode-clamped multilevel

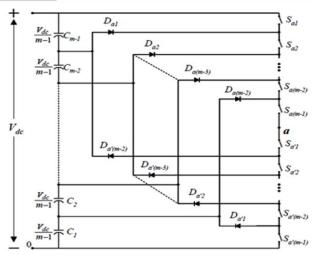

inverter employs clamping diodes and cascaded dc capacitors to produce ac voltage waveforms with multiple levels. However, as the number of levels has increased the number of clamping diodes, switching devices and dc capacitors also increases, thus the circuit configuration becomes more complicated. In general, for an *m*-level diode clamped inverter, for each  $\log 2(m-1)$  switching devices, (m-1) \* (m-2) clamping diodes and (m-1) dc link capacitors are required. In NPC topology, number of blocking diodes is quadratically related to the number of levels in the output voltage waveform. However, by increasing the number of voltage levels the quality of the output voltage has improved and the voltage waveform becomes closer to sinusoidal waveform. This means that for an *m*-level diode-clamped inverter has an *m*-levels in output phase voltage and a (2m-1) - levels in output line voltage waveform. The diode  $D_{a2}$  represented in Fig. 2.1 requires two diodes in series because it blocks two capacitor voltages, and the diode  $D_a(m-2)$  requires (m-2)series-connected diodes because it blocks (m-2) capacitor voltages.

Generally, the voltage across each capacitor for an *m*-level diode clamped inverter at steady state is Vdc/(m-1), where Vdc is dc bus voltage. Though, switching devices in NPC topology are required to block only a voltage level of Vdc but the clamping diodes require different ratings to block the reverse voltage. As the number of levels has increased the capacitor voltage balancing becomes a major problem.

#### **III. PROPOSED SYSTEM**

The input voltage level of the proposed basic unit is indicated in Fig. below. It presents novel cascaded multilevel inverters that can solve the total harmonic distortion reduction. By using a cascaded topology based on parallel connection of H bridge. The output voltage of CSLMI( $V_{out}$ ) is equal to the sum of output voltage of the all FSLMI. The maximum voltage rating on a switch is an important parameter which affects the inverter cost. Total

maximum voltage rating on unidirectional and bidirectional switches respectively are optimum level.

Therefore, the proposed CSLMI topology can be used in high voltage applications. The current rating of switches is another important parameter in the design of a converter. In the proposed topology, when the switches are turned off, the current tend to be zero. However, when the switches are turned on , the maximum current of the switches are equal to the load current.

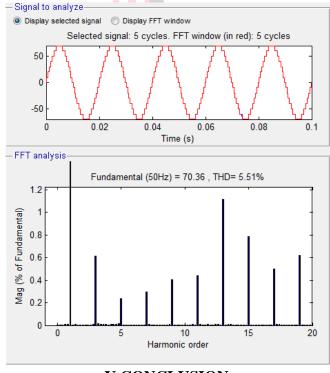

**IV.OUTPUT WAVEFORMS AND FFT**

ANALYSIS

## **V.CONCLUSION**

In this project, performance improvement of modified cascaded switch-ladder multi level inverter was described in this paper. The presented cascaded topology was optimized due to the extended feature of proposed topology. The main aim of optimization was generating maximum number of power electronics components and voltage rating on switches. Moreover, a good

approximation for the average power loss in the active and passive switches is given in simple expressions in terms of current, amplitude depth and power factor for typical conditions prevailing in CSLMI inverters. The results of comparisons indicated that the proposed cascaded topology could overcome the disadvantages of other structures.

#### REFERENCES

[1] K. Sivakumar, A. Das, R. Ramchand, C. Patel, and K. Gopakumar, "A five-level inverter scheme for a four-pole induction motor drive by feeding the identical voltage-profile windings from both sides," IEEE Trans. Ind. Electron., vol. 57, no. 8, pp. 2776–2784, Aug. 2010.

[2] C. Cecati, F. Ciancetta, and P. Siano, "A multilevel inverter for PV systems with fuzzy logic control," IEEE Trans. Ind. Electron., vol. 57, no. 12, pp. 4115–4125, Dec. 2010.

[3] R. Shalchi Alishah, S. H. Hosseini, M. Sabahi, E. Babaei, "A New General Multilevel Converter Topology Based on Cascaded Connection of Sub-Multilevel Units with Reduced Switching Components, DC Sources and Blocked Voltage by Switches," IEEE Trans. Ind. Electron., vol. 63, no. 11, pp. 7157–7164, Nov. 2016.

[4] C. Chen, G. P. Adam, S. Finney, J. Fletcher, B. Williams, "Hbridge modular multi-level converter: control strategy for improved DC fault ride-through capability without converter blocking," IET Power Electronics, vol. 8, no. 10, pp. 1996-2008, Aug. 2015.

[5] A. Lesnicar, R. Marquardt, "An innovative modular multilevel converter topology suitable for a wide power range," IEEE Power Tech. Conf. Proc., Bologna, Jun. 2003.

[6] R. Shalchi Alishah, D. Nazarpour, S. H. Hosseini, M. Sabahi, "Novel multilevel inverter topologies for medium and high-voltage applications with lower values of blocked voltage by switches," IET Power Electronics, vol. 7, no. 12, pp. 3062-3071, Oct. 2014.

[7] A. Nabae, I. Takahashi, and H. Akagi, "A new neutral-pointclamped PWM inverter," IEEE Trans. Ind. Appl., vol. 1A-17, no. 5, pp. 518–523, 1981.

[8] X. Yuan, I. Barbi, and H. Stemmler, "A New Diode Clamping Multilevel Inverter," IEEE/APEC, pp. 494-501, 1999.

[9] T. A. Meynard, H. Foch, F. Forest, C. Turpin, F. Richardeau, L. Delmas, G. Gateau, and E. Lefeuvre, "Multicell converters: Derived topologies," IEEE Trans. Ind. Electron., vol. 49, no. 5, pp. 978–987, Oct. 2002.

[10] E. Samadaei, S. Gholamian, A. Sheikholeslami, J. Adabi., "An Envelope Type (E-Type) Module: Asymmetric Multilevel Inverters with Reduced Components," IEEE Trans. Ind. Electron., vol. 63, no. 11, pp. 7148–7156, Nov. 2016.

[11] M. R. Banaei, E. Salary, H. Khounjahan, "A Ladder Multilevel Inverter Topology with Reduction of On-state Voltage Drop," Gazi University Journal of Science, vol. 1, no. 1, pp. 1-9, Mar. 2013.

[12] E. Babaei and S. H. Hosseini, "Charge balance control methods for asymmetrical cascade multilevel converters," Int. Conf. on Electrical Machines and Systems, Korea, pp. 74-79, 2007.

[13] S. Laali, K. Abbaszades and H. Lesani, "A new algorithm to determine the magnitudes of dc voltage sources in asymmetrical cascaded multilevel converters capable of using charge balance control methods," in Proc. ICEMS, Incheon, Korea, pp. 56-61, 2010.

[14] M. Manjrekar, T.A. Lipo, "A hybrid multilevel inverter topology for drive application," Proc. APEC, pp. 523-529, 1998.

[15] Y.-S. Lai, F. S. Shyu, "Topology for hybrid multilevel inverter," IEE Proc-Electro. Power Appl., vol. 149, no. 6, pp. 449-458, 2002.

[16] E. Babaei, "A cascade multilevel converter topology with reduced number of switches," IEEE Trans. Power Electron., vol. 23, no. 6, pp. 2657–2664, Nov. 2008.

[17] K. K. Gupta, S. Jain., "A multilevel Voltage Source Inverter (VSI) to maximize the number of levels in output waveform," Electrical Power and Energy Systems, vol. 44, no. 1, pp. 25–36, Jan. 2013.

[18] E. Babaei, S. Alilu, S. Laali, "A New General Topology for Cascaded Multilevel Inverters With Reduced Number of Components Based on Developed H-Bridge," IEEE Trans. Ind. Electron., vol. 61, no. 8, pp.3933-3939, 2014.

[19] E. Babaei, S. H. Hosseini, G. B. Gharehpetian, M. T. Haque, and M. Sabahi, "Reduction of DC voltage sources and switches in asymmetrical multilevel converters using a novel topology," J. Elect. Power Syst. Res, vol. 77, no. 8, pp. 1073–1085, Jun. 2007.

[20] J. Ebrahimi, E. Babaei, and G. B. Gharehpetian, "A new topology of cascaded multilevel converters with reduced number of components for high-voltage applications," IEEE Trans. Power Electron., vol. 26, no. 11, pp. 3119-3130, Nov. 2011.

[21] J. Ebrahimi, E. Babaei, and G.B. Gharehpetian, "A New Multilevel Converter Topology With Reduced Number of Power Electronic Components," IEEE Trans. Ind. Electron., vol. 59, no. 2, pp.655-667,

Feb. 2012.

[22] R. Shalchi Alishah, D. Nazarpour, S. H. Hosseini, M. Sabahi, "Reduction of Power Electronic Elements in Multilevel ConvertersUsing a New Cascade Structure," IEEE Trans. Ind. Electron., vol. 62, no. 1, pp.256-269, Jan. 2015.[23] S. P. Gautam, L. K. Sahu, S. Gupta, "Reduction in number of devices for symmetrical and asymmetrical multilevel inverters," IET Power Electronics, vol. 9, no. 4, pp. 698–709, Mar. 2016.

[24] Y. Sun, W. Xiong, M. Su, H. Dan, X. Li, J. Yang, "Modulation Strategies Based on Mathematical Construction Method for Multi- modular Matrix Converter," IEEE Trans. Power Electronics, vol. 31, no. 8, pp. 5423-34, Aug. 2016.

[25] Y. Sun, W. Xiong, M. Su, H. Dan, X. Li, J. Yang, "Topology and modulation for a new multilevel diode-clamped matrix converter," IEEE Trans. Power Electron., vol. 29, no. 12, pp. 6352-60, Dec. 2014.

[26] J. C. Rosas-Caro, J. M. Ramirez, F. Z. Peng, A. Valderrabano., "A DC- DC multilevel boost converter," IET Power Electron. vol. 3, no. 1, pp.129-137, Jan. 2010.

[27] C. Buccella, C. Cecati, M.G. Cimoroni, K. Razi, "Analytical Method for Pattern Generation in Five-Level Cascaded H-Bridge Inverter Using Selective Harmonic Elimination," IEEE Trans. Ind. Electron., vol. 61, no. 11, pp. 5811-5819, Nov. 2014.

[28] J. I. Leon, S. Kouro, S. Vazquez, R. Portillo, L. G. Franquelo, J. M.Carrasco, J. Rodriguez, "Multidimensional modulation technique for cascaded multilevel converters," IEEE Trans. Ind. Electron., vol. 58, no.2, pp. 412-420, Feb. 2011.