# Studies on Electrical Properties of $(Ta_2O_5)_{87.5}$ and $(TiO_2)_{12.5}$ Mix Oxide for MOSFET

Dinesh Kulkarni, Associate Professor, KGCE Karjat 410201 India, dineshkul1@gmail.com Rajashree Sarwadnya, Associate Professor, SGGS Nanded 431606 India, rvsarwadnya@gmail.com

Abstract - The scaling down of CMOS transistor requires replacement of conventional silicon dioxide (SiO<sub>2</sub>) layer with high K material for gate. In this current work mixed oxide of  $(Ta_2O_5)_{87.5}$  and  $(TiO_2)_{12.5}$  is chosen as alternative to SiO<sub>2</sub>. Capacitance, Fixed charges, Interface state density and Leakage current of that film is calculated. P-type single crystal silicon <100> is selected as substrate and DC reactive magnetron sputtering method with combination of Ta and Ti metal targets to deposit thin film. Oxygen is used as reactive gas along with Argon. The thickness of deposited film is in the range of 300±10 nm with substrate temperature  $600^{9}$ C. Agilent make 4284 A L-C-R meter along with Karlsuss wafer probe station is used for C-V measurement and Agilent 4155 model is used for I-V measurement. MOS capacitor has been fabricated with Aluminium as top electrode to perform bi-directional CV and IV analysis. Flat band voltage (V<sub>FB</sub>), Fixed charges (Q<sub>f</sub>), Interface state density (Dit') and Equivalent Oxide Thickness (EOT) are obtained from the bidirectional C-V analysis. The maximum dielectric constant achieved for MOS structure is 34.28 when Titanium is 12.5% and Tantalum is 87.5%.

#### Keywords — Capacitance, Sputtering, thin film, Fixed charges, Interface state density, Leakage current

## I. INTRODUCTION

The success of the semiconductor industry relies on the continuous improvement of integrated circuit performance. This improvement is achieved by reducing the dimensions of the key component of the circuit like MOSFET [1] [2]. The scaling of MOSFET was easily accomplished using SiO<sub>2</sub> as gate oxide layer but fundamental limit is the exponential increase of direct tunneling current as function of the SiO<sub>2</sub> thickness [12]. The concept of High-K replace is to reduce direct tunneling, and make the physical thickness of the gate dielectric larger, but keep the capacitance the same as an equivalent SiO<sub>2</sub> film. The requirement for the successful implementation of new high dielectric constant gate oxide materials in MOSFET application need to be fully understood before these materials can be adopted by industry [13]. The gate dielectric is used to isolate the gate terminal from the current carrying channel region. The dielectric material must be an insulator with a band gap greater than 5eV and there is an inverse relationship between dielectric constant and band gap. A closely related property is the height of the potential barrier presented to tunneling electrons from the conduction band and to tunneling holes from the valence band. Interface preparation and quality is important from layer growth point of view as well as performance point of view. There is inverse correlation exists between the thickness and quality of the interfacial layer and charge carrier mobility especially for electrons. There should be low interface trap density. The oxides must have a large Gibbs free energy of formation to prevent reaction with

silicon. Oxygen diffusion coefficients must be low as they will cause uncontrolled interfacial layer regrowth [14] [15]. Hence, this interface must be of the highest electrical quality, in terms of roughness and the absence of interface defects [11].

Ta<sub>2</sub>O<sub>5</sub>, also known as tantalum oxide is a high –dielectric constant (26-50) material with reasonably low leakage current  $(1*10^{-8} \text{A/cm}^2 \text{ at } 1 \text{ V})$  and high breakdown strength (5-6 MV/cm). It exists in both orthorhombic and hexagonal phases also known as low and high temperature forms. The low temperature form is known as  $\beta$ -Ta<sub>2</sub>O<sub>5</sub>, and the high temperature form is known as  $\alpha$ -Ta<sub>2</sub>O<sub>5</sub>. The transition point between these two forms has been reported as 1360°C. The transition is slow but reversible. The structures of both forms consist of chains built from octahedral and pentagonal bipyramidal polyhedra sharing opposite vertices. These chains are further joined by sharing edges to yield the 3D structure. Although the dielectric constant of Ta<sub>2</sub>O<sub>5</sub> is lower than other oxide films such as SrTiO<sub>3</sub>, Ba<sub>x</sub>Sr<sub>1-x</sub>TiO<sub>3</sub>, Pb<sub>x</sub>Zr<sub>1-x</sub>TiO<sub>3</sub> but Ta<sub>2</sub>O<sub>5</sub> can be deposited by PVD and CVD which is suitable for mass production. Excellent step coverage characteristic can be obtained by number of methods compatible with Si technology. One of the advantages of Ta<sub>2</sub>O<sub>5</sub> is by relevant annealing it is possible to improve the film stoichometry to make more abrupt interfaces to reduce structural non perfections and by this way to control and maximize dielectric. The higher K comes at the expense of a smaller band gap and lower conduction and valence band offsets between Si and Ta<sub>2</sub>O<sub>5</sub>. The band gap of  $Ta_2O_5$  is 4.5 [9] at the same time it has low

leakage current indicating that it has fewer problems than other materials.

$TiO_2$  also known as titanium oxide occurs in nature as minerals rutile, anatase and brookite, and additionally as two high pressure forms, a monoclinic and an orthorhombic form,  $TiO_2$  has high permittivity (30 for Anatase phase and 80 for Rutile phase) and also it has appreciable conduction band offset of 1.2 eV with Silicon.

### **II. EXPRIMENTAL**

#### A. Experiment

All the experimental work is aimed at the preparation of mixed oxide (Ta2O5)87.5 and (TiO2)12.5 thin film and to study the effect of process parameters and also the electrical properties of the prepared films [12]. The substrate material used for the deposition of mixed oxide (Ta2O5)87.5 and  $(TiO_2)_{12.5}$  films is P- type single crystal silicon with <100> orientation having a doping concentration of 0.2 x 10<sup>15</sup> to  $2.2 \times 10^{15} \text{ cm}^{-3}$  boron atoms (according to the doping information provided by the manufacturer). The 4" wafers are cut down into small pieces of rectangular/square shape before depositing the mixed oxide (Ta<sub>2</sub>O<sub>5</sub>)<sub>87.5</sub> and (TiO<sub>2</sub>)<sub>12.5</sub> thin film[8]. For MOS configuration Aluminium electrodes were deposited on the dielectric film using a mechanical mask. Aluminium electrodes have been deposited using thermal evaporation process. First the samples are subjected to ultrasonication for removing the contaminants like dust particles then cleaned in Piranha solution (a warm mixture of sulphuric acid ( $H_2SO_4$ ) and hydrogen peroxide ( $H_2O_2$ ) in 1:3 ratio) to remove any organic residues left on the substrate and to make it hydrophilic. Samples are rinsed in De Ionized (DI) water and then dipped in 5% HF solution to remove any native oxide  $(SiO_2)$  present on the samples. Finally the samples are rinsed in DI water and then flushed with dry air prior to loading in the deposition chamber.

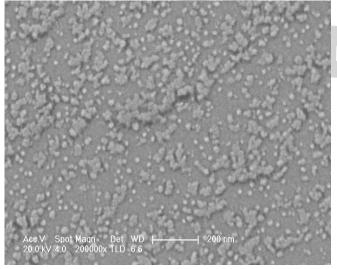

Fig.1 SEM image of mixed oxide film

The sputtering system used is a homemade deposition system, which is having a provision for the deposition of 3 materials. DC reactive magnetron sputtering has been used. The target material used is a Mosaic target, which is a combination of 3" diameter circular disc of Tantalum and small Titanium pieces having different areas. Argon (99.99% pure) and Oxygen (99.999% pure) are used as sputtering and reactive gas respectively. The sputtering chamber is evacuated to a base pressure of  $1.0* 10^{-5}$  mbar using a diffusion pump and rotary pump combination. The partial pressures of the two gases have been controlled by using mass flow controllers. The substrate to target distance is 6 cm.

#### B. Deposition of Film

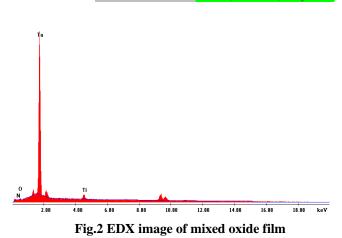

Before attempting the deposition of mixed oxide film, the process parameters have been optimized for deposition of Tantalum oxide films by depositing films at different current densities and different thicknesses at a base vacuum of 1.0\*10<sup>-5</sup> mbar, Oxygen partial pressure of 6\*10<sup>-4</sup> mbar and sputtering pressure of 4\*10<sup>-3</sup> mbar with substrate temperature of 600°C [4]. Then select the optimized parameter to deposit mix oxide film of desired composition. The mosaic target has Ta and Ti metal with area 87.5% and 12.5% respectively as sputtering yield is same for both the metal we get the required mixed oxide (Ta2O5)87.5 and (TiO<sub>2</sub>)<sub>12.5</sub> thin film. The area of the device or MOS capacitor used is 13278.57\*10<sup>-10</sup>m<sup>2</sup>. The metal contact used is aluminium. The topography of film is observed with SEM and the composition of the film is measured with EDX. The topography and the composition are as shown in fig.1, 2. From SEM and EDX results we checked that the film which we are getting is mixed oxide film with required element and composition. We measured the thickness of the films using profilometer. The thickness of prepared mixed oxide film is in the range of 300+-10 nm. Metal oxide semiconductor MOS Capacitor of mix-oxide (Ta<sub>2</sub>O 5)87.5  $(TiO_2)_{12.5}$  was prepared for the electrical studies.

For performing the Capacitance – Voltage measurements Agilent make 4284A L–C–R meter having operating frequency range from 20Hz to 1MHz is used along with a KarlSUSS make PM8 model probe station. Lab view

program is used to interface L-C-R meter with a Computer in which data is collected and also plotted simultaneously [6]. The options available in this program are setting the bias voltage range, probing signal frequency. The probe station is having a vacuum chuck to hold the sample firmly to avoid displacing of the sample while probing and also to provide proper electrical contact at the back side of the wafer. The tip of micro-manipulator is made of tungsten. The substrate doping concentration is obtained by measuring the minimum capacitance from the high frequency (1MHz) C-V curve of two samples for better comparison. The doping concentration of the p-type substrate is obtained as 4x10<sup>14</sup>cm<sup>-3</sup> boron atoms. Before performing the analysis of data from various samples, theoretical simulation for the C-V characteristics has been performed with a readily available MATLAB program. Various inputs provided to the program are thickness of the oxide film, metal-semiconductor work function difference value ( $\Phi$ ms), substrate doping concentration (Na), area of the capacitor (A) and also the dielectric constant (K) [7].

For performing the bi directional Capacitance-Voltage scan on MOS capacitor an alternating voltage of 5mV amplitude is super imposed onto a DC voltage, which is swept from accumulation region to inversion region (i.e. from - voltage to + voltage) and again from inversion to accumulation. The range of the DC voltage as well as the DC voltage step value is varied between different samples to get the best possible curves. The bi directional C-V curves for the film with AC voltage = 5mV, frequency = 1MHz has studied. The bi directional C–V scan performed on film has a finite hysteresis and among the factors which cause the hysteresis in the bi directional C-V the fixed charges (either positive or negative) which are close to the oxide interface. We have observed both kinds of charges in our study and the magnitudes of the fixed charge densities are calculated. [10]

#### Interface Trapped Charge Density (Dit')

The interface trapped charge density has been measured using the analytical technique given by Jakubowski and Iniewski [5]. In this technique we need to find out the capacitance value from the corresponding high frequency C– V curve and we need to use the following formula to find out the amount of Dit' which has a unit of  $cm^{-2}eV^{-1}$ .

Dit'=Cmax

$$(\Delta UG'-\Delta UG)/q^2 A\Phi F$$

cm<sup>-2</sup> eV<sup>-1</sup>

(1)

A =Area of the MOS capacitor

$\Phi F$ =Fermi potential of the P type Si

Cmax=Maximum Capacitance from C-V Graph

$\Delta$ U'G=Difference of the gate voltages corresponding to the surface potential of (1+ $\Phi$ F/2) and (1+ $3\Phi$ F/2).

$\Delta$ UG=Difference of the gate voltages corresponding to the surface potentials of (1+ $\Phi$ F/2) and (1+ $3\Phi$ F/2) calculated from the curve.

From calculation the interface state density is  $20 \times 10^{30}$  cm<sup>-2</sup> eV<sup>-1</sup> for the deposited thin film .Interface state density is higher for thick film due to oxygen de passivation and defect generation at interface. The defects at the interface should be as low as possible.

#### Fixed Charge Density $(Q_f)$

Fixed charge is the inherent charge present with most of the oxides that may be thermally grown or deposited onto silicon. The fixed charge present in the oxide is found out from the shift in the flat band voltage value measured from the C–V curve and the analytical flat band voltage value[16]. In our work we found out that the fixed charge is negative. The fixed Oxide charge we got is  $7.3 \times 10^{11} \text{ cm}^{-2}$ .

#### Flat band Voltage (V<sub>FB</sub>) & Threshold Voltage (V<sub>TH</sub>)

The  $V_{FB}$  is the most important parameter for a MOSFET because it is the factor that decides the  $V_{TH}$  and also the amount and polarity of the fixed charges present in the gate oxide. The  $V_{FB}$  observed for the sample is 0.2648 V and  $V_{TH}$  is 0.43 V.

#### Equivalent Oxide Thickness (EOT)

A number used to compare performance of high-k dielectric MOS gates with performance of  $SiO_2$  based MOS gates. It shows thickness of  $SiO_2$  gate oxide needed to obtain the same gate capacitance as the one obtained with thicker than  $SiO_2$  dielectric featuring higher dielectric constant. The EOT observed for sample is 33.8nm.

#### Current–Voltage (I–V) Analysis

For performing the I–V analysis we used Agilent 4155 .The minimum leakage current density achieved is  $3.5 \times 10^{-7}$  A/cm<sup>2</sup>. The breakdown voltage considered above 45V corresponding to the field of 1.5 MV/cm. The leakage current is minimum and the breakdown voltage is high for film of 300nm.

#### III. CONCLUSION

Further scaling of MOSFET requires high k dielectric material.  $(Ta_2O_5)_{87.5}$  and  $(TiO_2)_{12.5}$  mixed oxide thin film obtain from DC reactive magnetron sputtering and annealing with 600<sup>o</sup>C is chosen. Detail electrical properties for MOS structure for that thin film has been studied. Annealing process shows effect on quality of the grown oxides and their interface with Si which is a direct result of the oxidation temperature. The fixed charge for that film is  $7.3 \times 10^{11} \text{ cm}^{-2}$ . The interface state density is  $20 \times 10^{30} \text{ cm}^{-2} \text{eV}^{-1}$  and EOT that achieved is 33.8 nm. From the I-V analysis the minimum leakage current density achieved is  $3.5 \times 10^{-7} \text{ A/cm}^2$ . The deposition of Ti into Ta<sub>2</sub>O<sub>5</sub> causes generation of negative oxide charge which reduces the existing positive charge in Ta<sub>2</sub>O<sub>5</sub> and that result in decrease of leakage current. The breakdown voltage is at 45V

corresponding to the field of 1.5 MV per cm. The high dielectric constant, low leakage current, high break down voltage, low interface trap charged density indicate that  $(Ta_2O_5)_{87.5}$  and  $(TiO_2)_{12.5}$  thin film are encouraging for the possibility of gate oxide layer for microelectronic applications.

#### ACKNOWLEDGMENT

The authors acknowledge Plasma processing lab Instrumentation engineering department of IISc Bangalore for their support.

#### **References**

- [1] R.F.Cava, W.F.Peck Jr and J.J.Krajewski, "Enhancment of the dielectric constant of Ta<sub>2</sub>O<sub>5</sub> substitution  $TiO_2$ , Letters to through with nature, Nature 377, 215-217, 21September 1995; doi:10.1038/377215a0.

- [2] J.Y.Gan, Y.C.Chang and T.B.Wu,"Dielectric property  $(TiO_2)_x$ - $(ta_2O_5)_{1-}$ xthinfilms", Appl. Phys. Lett. 72, 332, 19 January 1998; https://doi.org/10.1063/1.120746.

- [3] E. Atanassova, A Pascaleva,"Challenges of Ta2o5 as dielectric for Nano scale DRAMs", high-k Microelectronics reliability, Vol 47,Issue6,913-923, June 2007. https://doi.org/10.1016/j.microrel.2006.06.006.

- [4] Y .Taikaishi, M Saka ,S Kamiyama, H Suzuki and H ,Watanabe ,"Low temperature integrated process below 50<sup>°</sup>C for thin  $Ta_2O_5$  capacitor for giga bit DRAMs". Electron devices meetings iedm 94, Technical digest, ieee, published, 06, August, 2002, doi: 10.1109/IED M:1994.383294.

- [5] Andrzej Jakubowski, Krzysztof Iniewski, "Simple formulas for analysis of C-V characteristics of MIS capacitor", solid state electronics,volume26,issue8,755-756,August1983, https://doi.org/10.1016/0038-110/(83)90037-0.

- [6] J.A.Walls, A.J. Walton, J.M. Robertson, T.M. Crawford," Interpretation of Capacitance-Voltage curves for process fault diagnosis a machine learning expert system approach", ieee proceedings on Teststructure, Microelectronic Vol1. No1,174,Feb1988, doi:10.1109/ICMTS.1988.672956.

- [7] Hyun-Ju Kim, Jae-Sung Song, In-Sung Kim, sang-Su Kim,"Electrical characteristics of Ti-o/Ta2o5 thin film sputtered on Ta/Ti/Al2o3 substrate", Thin solid films,Vol 1,124-127,1 446, issue Jan 2004, https://doi.org/10.1016/S0040-6090(03)01306-3.

- [8] Yue Wang, Yi-Jian," Composition dependence of dielectric properties of  $(Ta_2O_5)_{1-x}(TiO_2)_x$

polycrystalline ceramics", Materials science and engineerin:B,vol99,issue3,221-225,25May2003, https://doi.org/10.10161S0921-5107(02)00539-1.

- [9] Ruyan Guo, Yijian Jiang, A S Bhalla," Processing and Annealing conditions on the dielectric properties of (Ta<sub>2</sub>O<sub>5</sub>)<sub>0.92</sub>(TiO<sub>2</sub>)<sub>0.08</sub> ceramics", Materials Letters, Vol 57,issue 2,270-274,Dec 2002. https://doi.org/10.1016/S0167-577X(02)00777-2.

- [10] P S Dobal, R S Katiyar, Y Jiang, R Gou, A S Bhalla, "Micro Raman scattering and X Ray diffraction studies of  $(Ta_2O_5)_{1-x}(TiO_2)_x$  ceramics", Journal of Applied Physics, Vol 87, issue 12,8688, March 2000, https://doi.org/10.1063/1.373597.

- [11] A Cappellani, J L Keddie, N P Barradas, S M Jackson, "Processing and Characterization of sol gel deposited Ta<sub>2</sub>O<sub>5</sub> and TiO<sub>2</sub>-Ta<sub>2</sub>O<sub>5</sub> dielectric thin film", Solid state electronics. vol 43.issue 6.1095-1099.June 1999, https://doi.org 10.1016/S0038-1101(99)00031-3.

- [12] Mo Wu, Y I Alivov, Hadis Morkoc, "High K dielectrics and advanced channel concept for si MOSFET", Journal of material science: Materials in electronics,Vol 19.issue 10,915-951,Oct 2008,doi:10.1007/S10854-008-9713-2.

- [13] M Hirose, M Kon, W Mizubayasni, H Murakami, K Shibahara, S Miyazaki, "Fundamental limit of gate oxide thickness scaling in advanced MOSFET ", Semiconductor science and Technology, vol 15, issue 5,485, March 2000, https://doi.org/10.1088/0268-1242/15/5/308.

- [14] M Houssa , L Pantisano, L A Ragnarsson, R Degraeve, T Schram, G Pourtois, S De Gendt, G Groeseneken, M M Heyns,"Electrical proparties of high k gate dielectrics: Chalenges, current issues and possible solutions", Material science and engineering:R:Reports,vol 5,issue4-6,37-85,30April2006

,https://doi.org/10.1016/j.mser.2006.04.001.

- [15] R Chau, S Datta, M Doczy, B Doyle, J Kavalieros, M Metz,"High k metal gate stack and its MOSFET Characteristics", ieee electron device letters,vol25,issue6,408-410,June2004, doi:10.1109/LED.2004.828570.

- [16] Masahiko Hiratani, Kazuyoshi Torii, Yasuhiro Shimamoto, Shin-Ichi saito,"Built in interface in high k gate stacks", Applied surface science ,vol216,issue1-4,208-214,30June 2003.https://doi.org/10.1016/S0169-4332.