# Review paper on Convolutional encoder for different code rate based on FPGA

<sup>1</sup>S.D.Giri, <sup>2</sup>P.P.Patil, <sup>3</sup>A.R.Salunke

<sup>1,2,3</sup>Dept. of Electronics & Telecommunication, JNEC, Aurangabad, INDIA. <sup>1</sup>sunitagiri@jnec.ac.in, <sup>2</sup>patil.pratibha91@gmail.com, <sup>3</sup>aartisalunke@jnec.ac.in

Abstract- In this paper, in OFDM baseband processing systems a modified FPGA schemes using Vivado2016.1 for the Convolutional encoder is presented. The proposed design shows Convolutional encoder for different rate. The Convolutional encoder is finite state machine which contain a memory of past inputs and also a finite number of different states. Convolutional codes as well as other codes are used for correct bit errors at the receiver, are called Forward Error Correction (FEC). FEC schemes are an essential component of wireless communication systems (such as 802.11).

Keywords- Convolutional encoder, data rates, FPGA, VHDL, Vivado 2016.1.

### I. INTRODUCTION

Coding is a technique where redundancy is added to original bit sequence to increase the reliability of the communication. There are many types of coding techniques used to correct different error. Convolutional encoding method using Vivado 2016.1, a good technique used for correcting errors that occur during data transmission. Convolution code is one of the most important for error controlling performance. Convolutional encoder outputs are associated with the encoded elements at present and also affected by past elements. These codes plays a role in lowlatency applications such as speech transmission. (Yan Sun1. Zhizhong Ding2,2012)[1],(A.Msir,F. Monteiro, 2004), (Zafar Iqbal, Saeid Nooshabadi, Heung-No Lee,2012) [2]Convolutional codes are defined by following parameters; (n,k,m,L).

- n = number of output bits

- k = number of input bits

- m = number of memory registers

- L = constraint length[2]

Code Rate is the ratio of number of input bits to the number of output bits (k/n). Constant length is the number of delay elements in the Convolutional coding[3]. For example, L= 3, there are two delaying elements. Where, n>k. The quantity k/n is called as code rate and it is a measure of the efficiency of the code. Commonly k and n parameters ranging from 1 to 8, m from 2 to 10 and the code rate from 1/8 to 7/8 except for deep space.

Constraint Length, L = k (m-1)

The constraint length L represents the number of bits in the encoder memory that affect the generation of the n output

bits. The constraint length L is also referred to by the capital letter K.

### **II. METHOD**

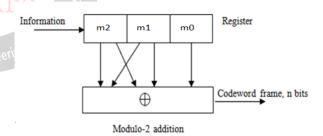

In Convolutional Encoder shifting is done by using shift registers. Delays can also be used in place of shift registers. Result outs as coded bit stream. Figure 1 shows the block schematic of a generalized Convolutional encoder. The structure of Convolutional code is simple. There are m memory register and n mod-2 adder to represent the n output bits.[4]

Figure 1: Basic Convolutional encoder

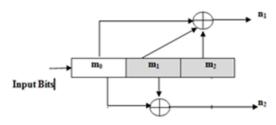

A. Rate 1/2

Figure 2: 1/2 Code rate Encoder

If initially Input=0 and m0=0, m1=0, m2=0

So, Output=00

Input=1, 1 is shifted to m0

m0=1, m1=0, m2=0

Thus, Output=11 and so on.

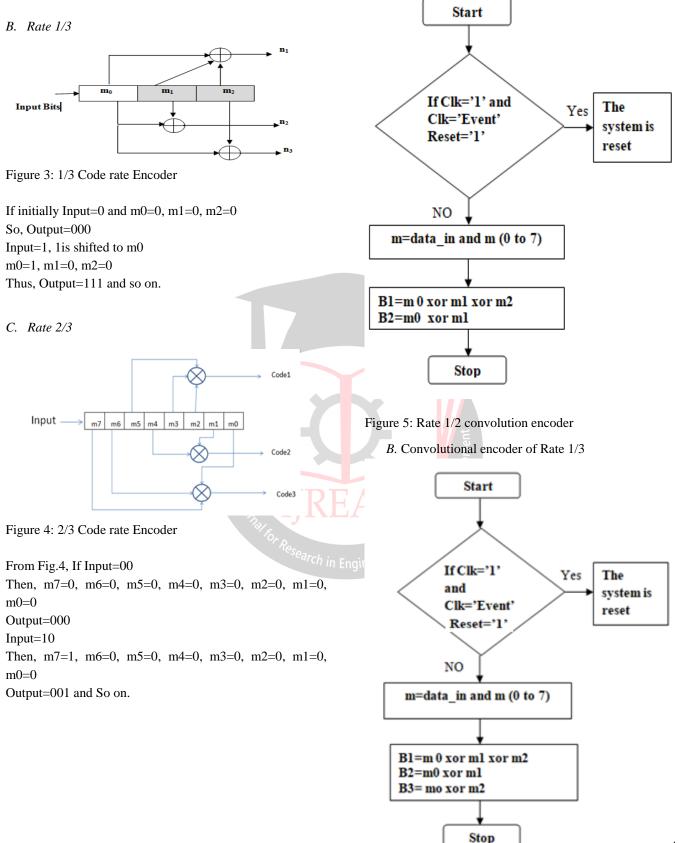

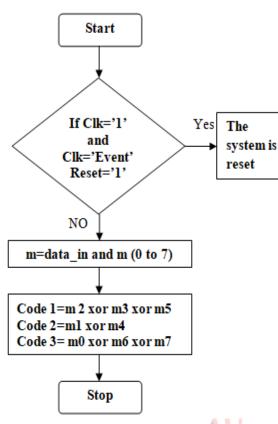

### **III.**WORKFLOW FOR DIFFERENT CODE RATE

A. Convolutional encoder of Rate 1/2

Figure 6: Rate 1/3 convolution encoder

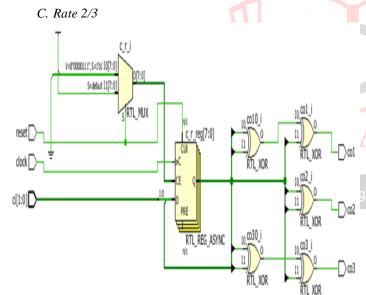

### C.CONVOLUTIONAL ENCODER OF RATE 2/3

Figure.7: Rate 2/3 convolution encoder

If 2-bit input is applied to encoder, it generates 3-bits as output according to given polynomial. Encoder consists of 1-bit Shift Registers and XOR gates.

Above workflow describes the design of Convolutional encoder. It shows conditions to perform designing.

### **IV. RESULTS AND RTL SCHEMATICS**

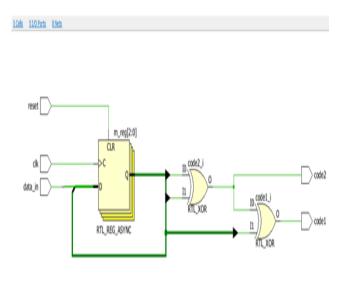

Figure.8 :( i) RTL Schematic for <sup>1</sup>/<sub>2</sub>

Figure.8: (ii) Result waveform for Rate <sup>1</sup>/<sub>2</sub>

Fig (8-i) shows RTL Schematic for the rate 1/2 and Fig. (8-ii) shows waveform for rate 1/2 Convolutional encoder

In above waveform of encoder here Clock is used for Synchronization. Reset is used for Initializing all the blocks. All inputs to the block are synchronized at rising edge of the clock. At every rising edge of clock pulse the system accepts new value of data and processes according to algorithm implemented and produces the output at next rising edge of clock. In the waveform initially code1 and Code2 is 0. Code1 is 1 for 2 to 4  $\mu$ s and code2 is 1 for 2 to 5  $\mu$ s and it again becomes 0.

The output is converted into

O- 0(00) I -3(11).

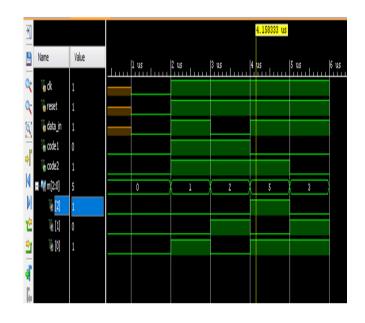

## earch in Engineer B. Rate 1/3

Figure 9: (i) RTL Schematic for 1/3

Figure 9: For data rate 1/3 (i) RTL Schematic (ii) Result shows waveform for rate 1/3 Convolutional encoder The output is converted into

# I -7(111)

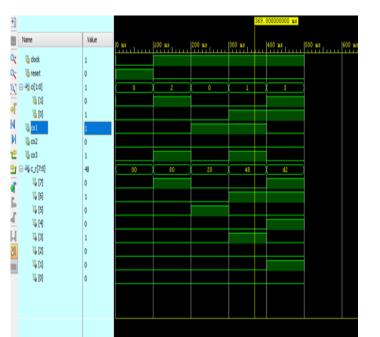

Figure 9 :( ii) Result waveform for Rate 1/3

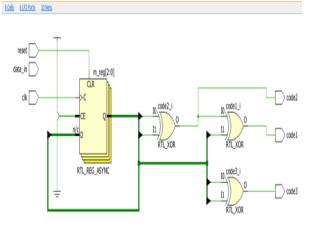

Figure10 :(i) RTL Schematic for Encoder 2/3

Figure10: (ii) Result waveform for Rate2/3 Figure10: For data rate 2/3 (i) RTL Schematic (ii) Result waveform. The output is converted into O0- 0(000) 10 -1(001)

Figure 11: FGPA Implementation

### **V. CONCLUSIONS**

This paper presents design of the structure of Convolutional code to reduce the influence from multi path and channel noise. Such a system can achieve flexibility with regard to changing data rates, increasing range, and increasing diversity, while offering efficient resource utilization.

This design is capable of transmitting data, in air errors and noise are tried to be minimized by using channel coding technique. The use of error-correcting codes has proven to be an effective way to overcome data corruption in digital communication channels. The data speed can be increased by using different combinations of encoding and modulation techniques.

### REFERENCES

[1].*Rolf* Johannesson and Kamil Sh. Zigangirov. *Fundamentals of Convolutional Coding*. IEEE Press, 1998.

[2].Lee, and L.H.C., "New rate-compatible punctured convolutional codes for Viterbit Decoding", IEEE Transactions on communications volume 42 Issue: 12, Dec.

[3].JohnG. Proakis, "Digital Communication" 3<sup>rd</sup> edition McGraw hill 1995.

[4].*Keshab K. Parhi*, "VLSI Digital Signal Processing Systems Design and Implementation".John wiley,1999.

[5].H.M.H.Dawid and G. Fettweis, "Viterbi Decoding: System Design and Implementation". IEEE trans. very large scale integration.(VLSI)syst,vol.4,no.1,pp.17-31,mar 1996.

[6].Wong, Y.S.et.al "Implementation of convolutional encoder and Viterbi decoder using VHDL" IEEE Tran. on Inform. Theory, Pp. 22-25, Nov. 2009.

[7] H. J. Kang and I. C. Park, "A high-speed and lowlatency Reed– Solomon decoder based on a dual-line structure," in Proc. IEEE Int. Conf. Acoust., Speech, Signal Process., May 2002, vol. 3, pp. 3180–3183

[8] Berlekamp, E.R. The technology of error-correcting codes. Proceedings of the IEEE, 1980,68, 564-93.

[9] Bhargava, V.K. Forward error correction schemes for digital communications. IEEE Commun. Mag. 1983,21, 11-19.

[10] S. K. Hasnain, and Azam Beg and "Performance Analysis of Viterbi Decoder Using a DSP Technique", 8th IEEE International Multitopic Conference(ITMIC'04), Dec 2004,pp.201-207.

[11] S. Brazza O. Winstin F.

[11] S. Ranpara, On a Viterbi Decoder Design for LowPower Dissipation, M.S. Thesis, Dept. of Electrical and Computer Eng., Virginia Polytechnic Institute and State University, April 1999.

[12]Benedetto, Sergio, and Guido Montorsi. "<u>Role of</u> recursive convolutional codes in turbo codes." Electronics Letters 31.11 (1995): 858-859.

[13] Eberspächer J. et al. GSM-architecture, protocols and services. – John Wiley & Sons, 2008. - p.97

[14] 3rd Generation Partnership Project (September 2012). "3GGP TS45.001: Technical Specification Group GSM/EDGE Radio Access Network; Physical layer on the radio path; General description". Retrieved 2013-07-20.

[15] Halonen, Timo, Javier Romero, and Juan Melero, eds. GSM, GPRS and EDGE performance: evolution towards 3G/UMTS. John Wiley & Sons, 2004. - p. 430