# A Novel Pseudo PMOS Integrated Low Power Inductor less LNA used for Wireless Receiver

Malika Jain, Research Scholar JIMS University, Jaipur, India, jainmalika@gmail.com Ramesh Bharti, Professor, JIMS University, Jaipur, India, ramesh.bharti@jims.org

Abstract A performance study of a novel Pseudo-PMOS integrated LNA used for wireless receiver with zero static power dissipation is presented in this paper. The simulation of power and performance measurement, as well as comparisons with existing systems used in wireless receivers, is the key focus. The commonly used devices use a lot of power and aren't reliable enough for long-term. The conventional device has low slew rate, high power consumption, and nonlinear characteristics; however, due to zero static power, less load capacitance on input signals, faster switching, less transistors, and higher circuit density in this novel design, the device has a better slew rate and piecewise linear characteristics, and is seen consuming very low power in the order of 0.004mW. The Maximum Gain of 14 dB at 2 .3 GHz is obtained for a given circuit. Noise figure of the device is obtained as 0.24dB at 2.3-2.5 GHz range. The proposed circuit uses less total power per cycle, improves operation speed, is reasonably linear, and is easy to implement.

Keywords — LNA, low power, simulation, Pseudo-PMOS, gain, noise factor, slew rate

# I. INTRODUCTION

In almost all wireless communication systems, the Low Noise Amplifier is a critical factor. It is important for reducing the amount of noise in the signal received from the antenna [1]. The gain of this amplifier is also crucial since it lowers the noise figure of subsequent levels [2]. Friis' formula mathematically illustrates this principle as follows:

$$F_{total} = F_1 + \frac{F_2 - 1}{G_1} + \frac{F_3 - 1}{G_1 G_2} + \frac{F_4 - 1}{G_1 G_2 G_3} + \cdots \prod R$$

$$+ \frac{F_n - 1}{G_1 G_2 \dots G_{n-1}}$$

Where,  $F_{total}$  denotes the system's total noise figure, n the number of stages, and G the stage's gain [3][4]. Wireless receiver's operating in the GHz range would benefit greatly from the proposed design.

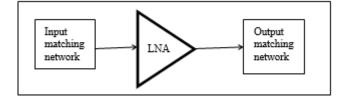

Amplifier, input matching network, and output matching network are the three key stages of the basic LNA architecture. Figure 1 illustrates this. Stability, low noise figure, and high gain are all features of this amplifier [5][6]. Maximum power transfer is ensured by the input and output matching networks.

Fig. 1 Basic LNA architecture

To design LNA, extensive research and a variety of approaches have been suggested. Inductor, filter, common gate based Distributed amplifiers and shunt resistor based feedback amplifiers are some of the techniques widely used to achieve wideband input matching for LNA [7][8][9]. However, these techniques can have a number of drawbacks, including a large chip area, high power consumption, and insufficient NF[10].

This research paper describes a new pseudo PMOS-based inductor less LNA design that aims for small size, low static power and small size with significant gain. In order to achieve all mentioned above a novel Pseudo PMOS integrated low power inductor less LNA for wireless receiver with adequate voltage gain, and high linearity, with noise cancelling techniques (shunt feedback) is used in this proposed design.

### **II.** CONVENTIONAL LNA

In general, feedback is a popular technique used in the design of wideband amplifiers to achieve input matching. LNA can achieve a very wideband (from 0-22 GHz) with less power consumed also significant high gain using resistive feedback [11][12]. The approach uses negative feedback and has limit to lower amplifier's input resistance and increase its bandwidth by lowering the tradeoff gain[13] [14]. In comparison to other techniques, resistive feedback LNAs configuration can achieve a smaller chip area since no or less inductors are added and utilized[15][16].

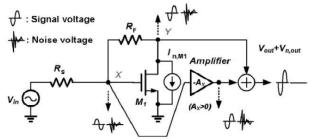

Noise cancellation technique is used to create noises with opposite polarities in the different paths and cancel out

each other at the output. This method used for noise cancellation as well as impedance matching. Figure 2 demonstrates a noise cancelling technique-based simplified resistive shunt feedback LNA. This LNA is made up of a transistor M1, an RF resistor, and a gain of AX (AX>0) feed forward voltage amplifier [17]. The input impedance Zin is designed to fit the source impedance Rs for optimum power transfer [18].

Fig. 2 Noise cancellation technique

# **III. PSEUDO PMOS**

Pseudo-PMOS logic is a ratioed logic that realizes the logic feature by using a grounded PMOS as a load for pull-up network and Driver circuit is made up of NMOS pull-down network[19][20].

This logic is very important and low component count as it only uses N+1 MOSFETs as compared with 2N MOSFETs used in CMOS technology. Another merit of these type of circuits are that It has less load capacitance and fast switching as compared with another technologies [21]. The high output voltage level for any gate in pseudo-NMOS logic is VDD. As the VDD and ground has direct path through the PMOS transistor, the only major disadvantage of this logic is its extremely high static power consumption [22] [23].

## **IV. CIRCUIT DESCRIPTION**

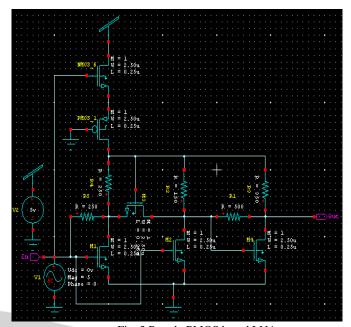

As shown in Fig.3, the proposed Pseudo PMOS inductorless LNA uses a resistive feedback topology for noise cancellation and output buffer levels. The input is connected by  $R_s$ , which has a source impedance of 50 ohm.  $R_{F1}$  is a shunt feedback resistor in the noise cancelling stage that is used for wideband wireless receivers for detecting the signal and noise of the input MOSFETs  $M_1$ ,  $M_2$  and  $M_3$  to integrate the signal and deduct the noise of  $M_1$ . The load resistors  $R_{D1}$  and  $R_{D2}$  are being used to subtract the noise at  $M_2$ 's drain, the signal polarities at  $M_1$  and  $M_2$ 's drains must be in phase.

The source follower is often used in wireless amplifiers to achieve wideband output matching. Source followers, on the other hand, have poor driving capacity and use a lot of voltage headroom in low voltage applications. In this novel design LNA is made up of  $M_4$ ,  $R_{F2}$ , and  $R_{D4}$  and uses a resistive shunt feedback output stage further the circuit is built using a pseudo-PMOS technology which contains grounded gate PMOS . One NMOS is located just above the PMOS as mentioned will act as a switch, ON only when input is applied otherwise OFF. Hence, preventing the circuit from static power dissipation. The circuit diagram of proposed design is given in Figure. 3

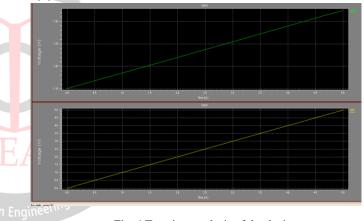

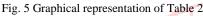

Fig. 3 Pseudo PMOS based LNA The transient analysis is shown in Fig.4. Input signal shows linear variation with time as depicted by yellow

graph. Similarly output also varies linearly with the input variation (indicated by the green graph). This shows that device is reasonably linear.

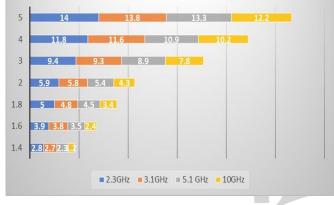

The parameters used to design the circuit is given in the Table 1 also the variation of voltage gain at different frequencies and at different levels are tabulated in the Table 2

Table: 1 Parameter description

| Parameters      | Values |

|-----------------|--------|

| R <sub>F1</sub> | 250Ω   |

| R <sub>F2</sub> | 500 Ω  |

| R <sub>D1</sub> | 250 Ω  |

| R <sub>D2</sub> | 150 Ω  |

| R <sub>D4</sub> | 350 Ω  |

#### Table 2 Voltage and Gain variations

| Voltage | 2.3GHz | 3.1GHz | 5.1GHZ | 10GHz |

|---------|--------|--------|--------|-------|

| level   |        |        |        |       |

| 1.4     | 2.8    | 2.7    | 2.3    | 1.2   |

| 1.6     | 3.9    | 3.8    | 3.5    | 2.4   |

| 1.8     | 5      | 4.8    | 4.5    | 3.4   |

| 2.3     | 5.9    | 5.8    | 5.4    | 4.3   |

| 3.3     | 9.4    | 9.3    | 8.9    | 7.8   |

| 4.3     | 11.8   | 11.6   | 10.9   | 10.2  |

| 5.0     | 14     | 13.8   | 13.3   | 12.2  |

The data presented above is represented graphically in Figure 5

# Variation of Gain with Input Voltage

Fig. 7 Noise analysis of the given circuit

Table 3 Comparison with existing divces

| [Ref]              | Power (mW) | Gain (dB) | N.F (dB) | F0 (GHz)   |

|--------------------|------------|-----------|----------|------------|

| [6]                | 30         | 22        | 3.5      | 1.5        |

| [7]                | 12         | 22        | 2.5      | 2.5        |

| [8]                | 22.4       | 19.8      | 3        | 2.4        |

| [9]                | 7.2        | 15        | 2.2      | 2.4        |

| [10]               | 4.5        | 13.4      | 3        | 2.5        |

| [11]               | -          | 15.9      | 2.88     | 2.45       |

| [12]               | 13.2       | 11        | 2.2      | 2.4        |

| [13]               | 7.33       | 20.34     | 1.98     | 2.4-2.5    |

| [14]               | 4.49       | 26.48     | 1.044    | 2.45       |

| Proposed<br>design | 0.004      | 14        | 0.24     | 2.4-2.5GHz |

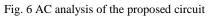

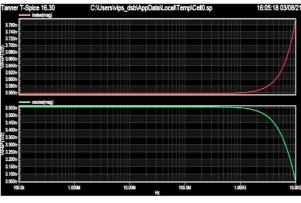

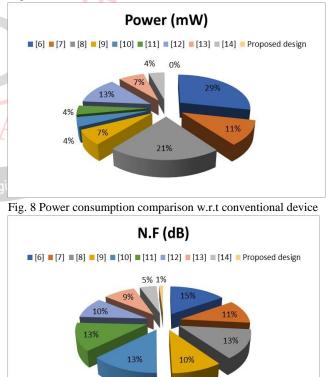

Comparison of the different parameters of LNA with the existing design has been done and presented in the Table 3 and its comparisons are also shown in Figure 8 and figure 9. From the parameters shown above it is inference that the proposed design consumes very less power in order of 0.004mW which is almost negligible as compared to other designs with a moderate gain of 14 dB with a NF of 0.24dB which is 1% as compared to the conventional designs in the range of 2.4- 2.5 GHz the ac analysis and the noise analysis of the device is shown in Figure 6 and Figure7.

Fig. 9 Noise figure Comparison w.r.t conventional devices **V. RESULT**

Proposed pseudo PMOS LNA design simulation are carried out in Tanner Tool of Mentor Graphics using 0.35  $\mu m$  CMOS process technology. This section summarizes the

different findings obtained. When we compare the latest design to the old design, we get the following findings.

(a) The number of MOSFETs in traditional devices is 10 in [1], 8 in [2], but only 6 in the latest model. As a result, major part savings are realized, resulting in cost savings.

(b) Static power is nearly zero. And the average power consumption obtain through the simulation is 0.004mW and the is included in the Appendix as a reference

(c) The new approach does not use a capacitor.

(d) In the traditional system, there are 4-3 current sources deployed, while in the modern device, there are none.

(e) The simulation of the circuit is carried out for different input voltage levels for wireless receivers and it has been found that for a particular voltage the gain gradually decreases as frequency increases from 1GHz to 10GHz.

(f) Also it is observed that the Max Gain of 14 dB at 2.3 GHz for input voltage of 5Vwhich gradually decrease to 13.8 at 3GHz and 13.2 to 5GHz and minimum 12.2 at 10GHz. This shows the Voltage gain decreases gradually when operating in a high frequency which may be due to intervening of parasitic capacitance at high frequency.

(g) The Noise figure for the simulated circuit is obtained as 0.24dB at 2.3 GHz

# VI. CONCLUSION

A new Pseudo PMOS based LNA is proposed in this paper. The conventional device has low slew rate, high power consumption, and nonlinear characteristics; however, due to zero static power, less load capacitance on input signals, faster switching, less transistors, and higher circuit density in this novel design, the device has a better slew rate and piecewise linear characteristics, and is seen consuming very low power. Excellence of the method has been proven by computer simulations findings and comparisons with test data and simulations at transistor level. The analytical analysis is in line with all the findings.

# **VII. FUTURE SCOPE**

A new system based on PP-LNA is proposed in this novel design. The PP that was implemented is a useful building block that simplifies the design of linear analogue systems. It also uses a small amount of energy. The slew rate has seen a noticeable change. The observed production is extremely linear. The proposed design's straightforward architecture and low component count are significant advantages. As a result, it's ideal for a wide-band wireless receiver. This research could be expanded to include additional changes in terms of power and scale, as well as wiring and layout characteristics.

### REFERENCES

- A. Boutejdar, O. abbas, B. Edmun, "High-performance wide stop band low-pass filter using a vertically coupled DGS- DMS-resonators and inter digital capacitor", Microwave and Optical Technology Letters, June 2016, vol. 58 Issue 6, pp1514-1516

- [2] A Sedra, K. A Smith (1970). Second generation conveyor and its applications, IEEE Trans. Conductions on Circuit Theory. 1970, CT-17,pp: 132-134.

- [3] W Chiu, S I Liu, H W Tsao, J J Chen (1996). CMOS differential difference current conveyors and their applications. IEEE Proceedings G: Circuits Devices Systems, 1996, 43(2), pp:91-96.

- [4] H O Elwan, A M Soliman (1997). Novel CMOS differential voltage current conveyor and its applications. IEEE Proceedings G: Circuits Devices Systems, 1997, 144(3),pp: 195-200.

- [5] EI. Adawy A A, Soliman A M, Elwan H O(2000). A novel fully differential current conveyor and applications for analog VLSI. IEEE Transaction on circuits and systems-II: Analog and digital signal processing, 2000, 47(4), pp:306~313.

- [6] P. Bergveld (1970), Development of an Ion-sensitive Solid- state Device for Neurophysiologic Measurements, IEEE Trans. Biomed. Eng.pp: 70-71.

- [7] Sergio Martinoia and Giuseppe Massobrio (2002), A Behaviour Macro-Model of the ISFET in SPICE, Sensors and Actuators B, pp:182-189.

- [8] B. Palan, F.V.Santos, and J.M.Karam (1999), New ISFET Sensor Interface Circuit for Biomedical Applications, Sensors and Actuators B, pp:63-68.

- [9] A. Morgenshtein, L. S. Boreysha and U. Dinnar (2004), CMOS Readout Circuitry for ISFET Micro- systems, Sensors and Actuators B, (97):122-131.

- [10] P. Whig, S. N. Ahmad, (2011) Performance analysis and frequency Compensation Technique for Low Power Water Quality Monitoring Device Using ISFET Sensor. International Journal of Mobile and Adhoc Network. pp 80- 84.

- [11] Ali, A. Khan, M. A., Hu, Z, "High selectivity low pass filter using negative-ε meta material resonators", Electronics Letters, vol. 43, Issue 9, pp. 528-530, April 2007.

- [12] Ali. Abid, Hu, Zirun, "Sharp cut-off and reduced size miniaturized metamaterial binomial micro strip low-pass filter", Microwave and Optical Technology Letters, vol. 49, Issue 10, pp. 2406-2409, October 2007.

- [13] P. Whig and S. N. Ahmad, "DVCC based readout circuitry for water quality monitoring system," International Journal of Computer Applications, vol. 49, pp. 1–7, 2012.

- [14] P. Bergveld, "Development of an ion-sensitive solid-state device for neurophysiologic measurements," IEEE Transactions on Biomedical Engineering, vol. 17, no. 1, pp. 70–71, 1970.

- [15] P.bergveld, "Thirty years of ISFETOLOGY: what happened in the past 30 years and what may happen in the next 30 years," Sensors and Actuators B, vol. 88, no. 1, pp. 1–20,2003

- [16] Y.-H. Chang, Y.-S. Lu, Y.-L. Hong, S. Gwo, and J. A. Yeh, "Highly sensitive pH sensing using an indium nitride ion- sensitive field-effect transistor," IEEE Sensors Journal, vol. 11, no. 5, pp. 1157–1161, 2011.

- [17] F. Kacar, A. Yesil, and A. Noori, "New CMOS realization of voltage differencing buffered amplifier and its biquad filter applications," Radio Engineering, vol. 21, no. 1, p. 333, 2012.

- [18] Synopsys, TCAD Sentaurus device user's manual VG-2012.06.1.

- [19] P. Whig and S. N. Ahmad, "On the performance of ISFET- based device for water quality monitoring," International Journal of Communications Network and System Sciences, vol. 1913, p. 709,2011.

- [20] P. Whig and S. N. Ahmad, "A CMOS integrated CC-ISFET device for water quality monitoring," International Journal of Computer Science Issues, vol. 9, no. 4, p. 1694,2012.

#### Power Results

vdd from time 0 to 5e-007

Average power consumed -> 4.142440e- 006 watts Max power 3.061053e-005 at time 4.04571e-007 Min power 3.143356e-011 at time 1.05483e-007 Setup 0.01 seconds Transient Analysis 0.48 seconds Overhead seconds ---Total ---Sēčonds